The circuit diagram and truth table is shown below.Ī clock pulse is given to the inputs of the AND Gate. This problem can be overcome by using a bistable SR flip-flop that can change outputs when certain invalid states are met, regardless of the condition of either the Set or the Reset inputs.įor this, a clocked S-R flip flop is designed by adding two AND gates to a basic NOR Gate flip flop.

The problems with S-R flip flops using NOR and NAND gate is the invalid state. If both the values of S and R are switched to 1, then the circuit remembers the value of S and R in their previous state. They are supposed to be compliments of each other. If both the values of S and R are switched to 0 it is an invalid state because the values of both Q and Q’ are 1. In both the states you can see that the outputs are just compliments of each other and that the value of Q follows the compliment value of S. Like the NOR Gate S-R flip flop, this one also has four states. The circuit of the S-R flip flop using NAND Gate and its truth table is shown below.įig.2 SR Flip-flop Using Nand gates Operation This is an invalid state because the values of both Q and Q’ are 0. If both the values of S and R are switched to 0, then the circuit remembers the value of S and R in their previous state. In both the states you can see that the outputs are just compliments of each other and that the value of Q follows the value of S.

By 3 Flip flop we get output as 2 3-1= 7 to 0.Fig.1 SR Flip-flop Using NOR gates Operationįrom the diagram it is evident that the flip flop has mainly four states. We get output(state changes) after every -ve edge clock pulse. Therefore, we get output(as down counting Q3(MSB) Q2 Q1(LSB) after 8th -ve edge triggered clock the output of the three Flip flops again becomes Q3 = 0, Q2 = 0, Q1 =0. Therefore, Flip flop 3 output is toggle when there is clock falling edge and Q’2=1 and Q’1 = 1. Similarly, Flip flop 3 toggle input(T) is connected to Q’2 and Q’1. Therefore, Flip Flop 2 output state Q 2 is toggle only when there is clock falling edge (i.e -ve edge triggering) and Q’ 1 =1. Flip-flop(FF) 2 toggle input(T2) is connected to Q’ 1. In simplified equation of K map we get T 1 = 1, therefore Flip flop 1 output Q 1 is toggle for every negative edge(because clock is negative edge triggered). Here -ve edge triggered clock is used for toggling purpose.Īs we see from characteristics table when T = 1, then toggling takes place and T =0 then it stores the output state. Timing diagram of 3 bit synchronous Down counter. Program for Binary To Decimal Conversion. Program for Decimal to Binary Conversion.

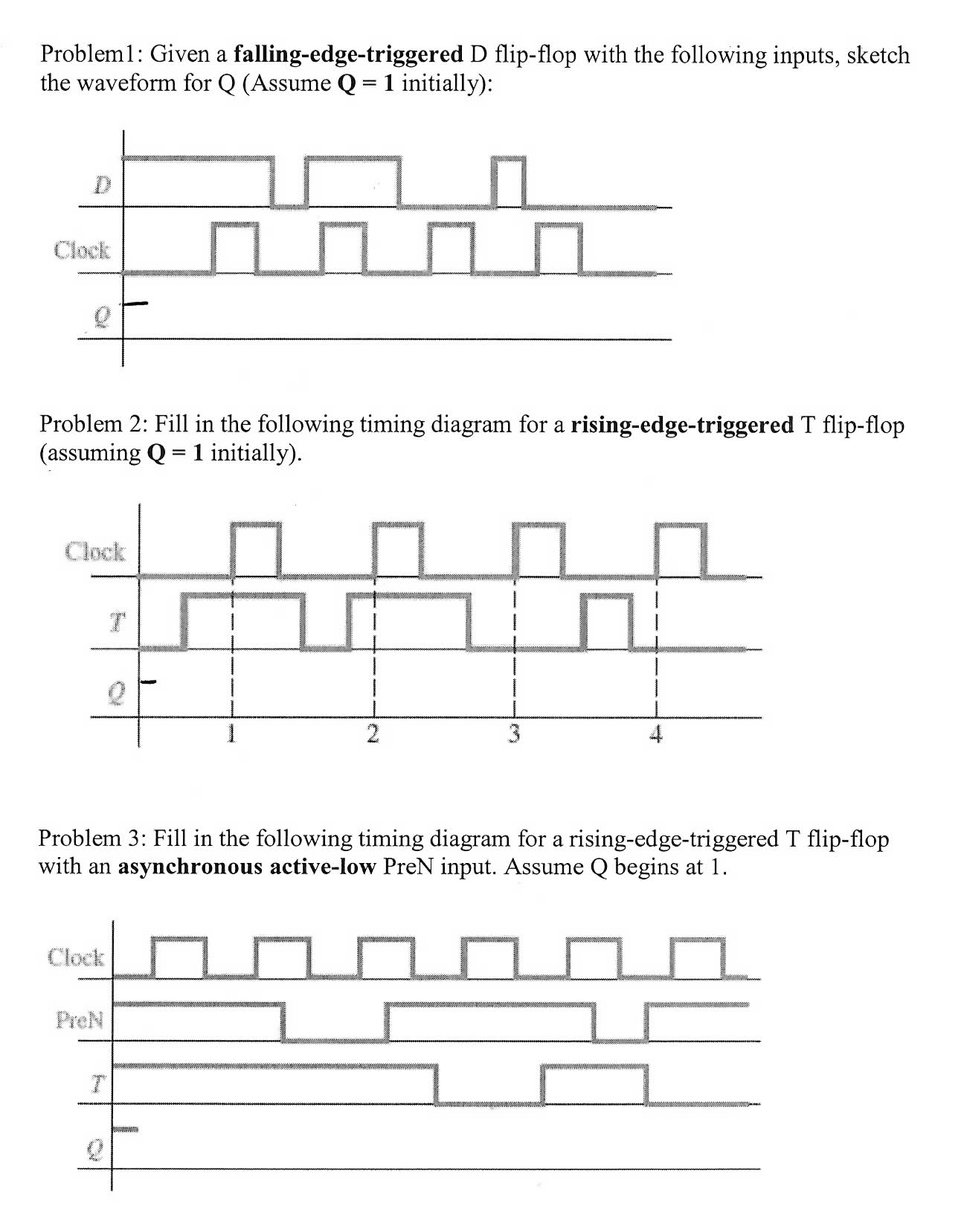

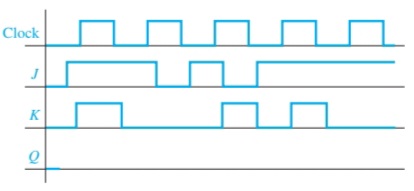

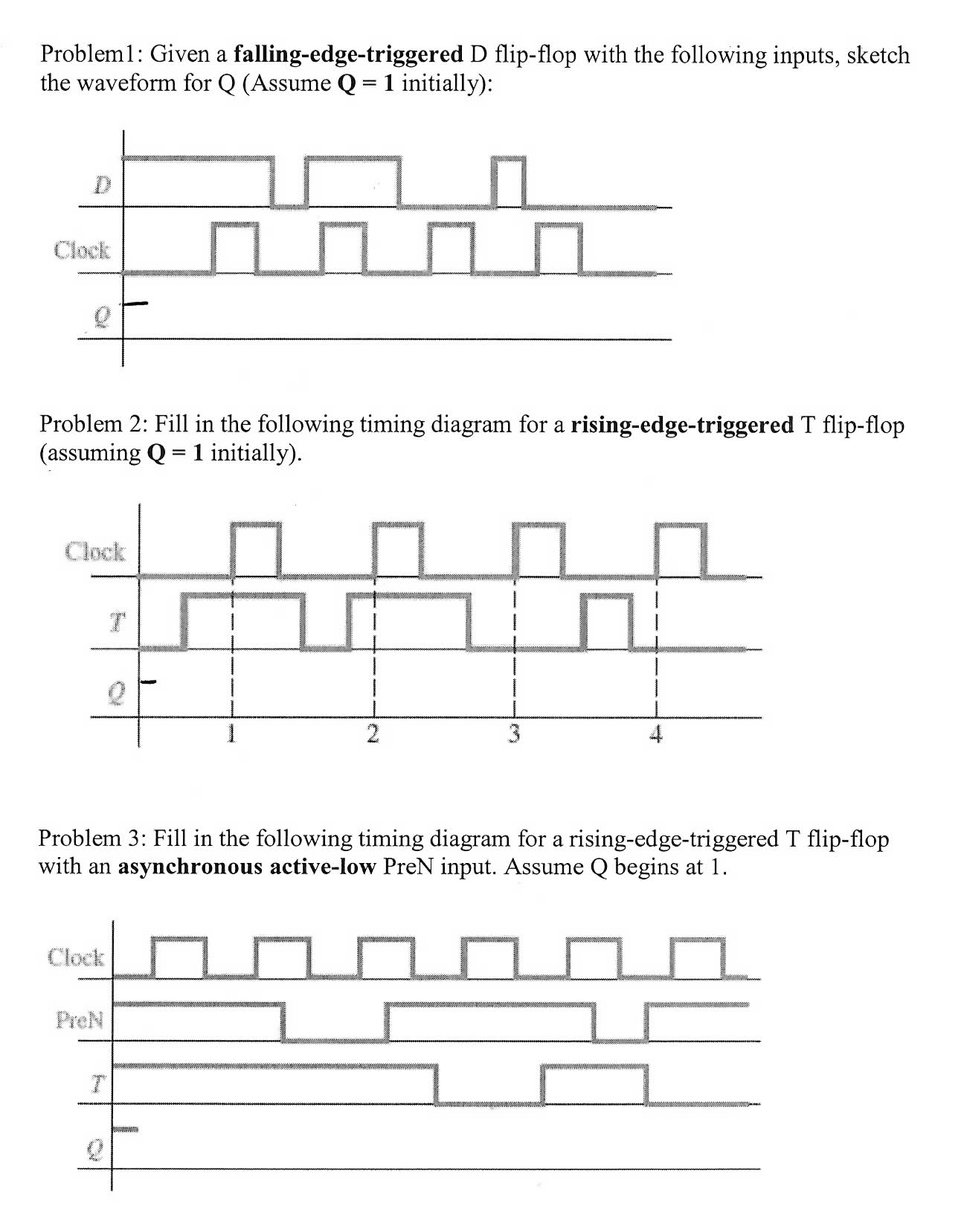

By 3 Flip flop we get output as 2 3-1= 7 to 0.Fig.1 SR Flip-flop Using NOR gates Operationįrom the diagram it is evident that the flip flop has mainly four states. We get output(state changes) after every -ve edge clock pulse. Therefore, we get output(as down counting Q3(MSB) Q2 Q1(LSB) after 8th -ve edge triggered clock the output of the three Flip flops again becomes Q3 = 0, Q2 = 0, Q1 =0. Therefore, Flip flop 3 output is toggle when there is clock falling edge and Q’2=1 and Q’1 = 1. Similarly, Flip flop 3 toggle input(T) is connected to Q’2 and Q’1. Therefore, Flip Flop 2 output state Q 2 is toggle only when there is clock falling edge (i.e -ve edge triggering) and Q’ 1 =1. Flip-flop(FF) 2 toggle input(T2) is connected to Q’ 1. In simplified equation of K map we get T 1 = 1, therefore Flip flop 1 output Q 1 is toggle for every negative edge(because clock is negative edge triggered). Here -ve edge triggered clock is used for toggling purpose.Īs we see from characteristics table when T = 1, then toggling takes place and T =0 then it stores the output state. Timing diagram of 3 bit synchronous Down counter. Program for Binary To Decimal Conversion. Program for Decimal to Binary Conversion. TIMING DIAGRAM EDGE TRIGGERED FLIP FLOP CODE

Code Converters – BCD(8421) to/from Excess-3. Code Converters – Binary to/from Gray Code. Universal Shift Register in Digital logic. Design 101 sequence detector (Mealy machine). Difference between Mealy machine and Moore machine. Program to Implement NFA with epsilon move to DFA Conversion. ISRO CS Syllabus for Scientist/Engineer Exam. ISRO CS Original Papers and Official Keys. GATE CS Original Papers and Official Keys.

0 kommentar(er)

0 kommentar(er)